提供多样的产品和服务,助您充分发挥产品的价值,助力业务腾飞

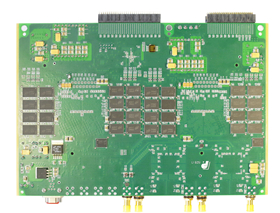

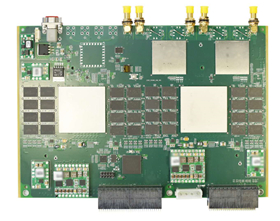

高速AD板由两片FPGA、2片ADC构成。FPGA_B接收2路ADC的原始波形数据,通过DDR3进行缓存,再由SRIO将原始波形数据发送到FPBA_A进行信号处理。FPGA_B可以将原始波形数据和FPGA_A处理后的波形数据通过PCIE发送到主机,实现波形的处理与采集功能。

对外接口包括一路PCIEx4链路、高速串行信号等。两片FPGA之间有高速串行接口以及LVDS接口。

为了便于同步,ADC的采样时钟由外部通过SMA提供、FPGA的调试接口采样菊花链方式串联1.8V JTAG ,配置方式为FAST BPI。

主要指标:

● 标准6U VPX板卡;

● A/D采样率:5 Gsps;

● A/D分辨率:10bit;

● 板内多片ADC可同步工作;

● FPGA型号:XC7VX690T, FPGA资源使用率:可大于70%;

● FPGA资源使用率:可大于70%;

● DDR3阵列:4组DDR3,每组8Gbyte @ 64bit;

● DDR3速率:≥ 1000 Mb/s;

● 数据接口:高速串口@6Gbps;

● 控制接口:x4 PCI-E;

● 温度范围:-55℃~70℃;

● 整板功耗:最大100W;

● 电路板规格:VPX标准板卡,主板6U×160mm,后I/O板6U×40mm,风冷散热。